# Chapter 5 Designing Combinational Systems (I)

## Overview (1/1)

- Large systems are usually designed by breaking them up into smaller subsystems

- We will first look at systems that consist of a number of identical blocks. (These are sometimes referred to as *iterative systems*.) Adders and other arithmetic functions are examples of this type of system

- Gate arrays are commonly available in three forms: *read only memory* (ROM), *programmable logic array* (PLA), and *programmable array logic* (PAL)

### Iterative Systems (1/1)

- When we add two numbers by hand, we add the two least significant bits (plus possibly a carry-in) to produce one bit of the sum and a carry to the next bit

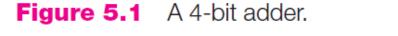

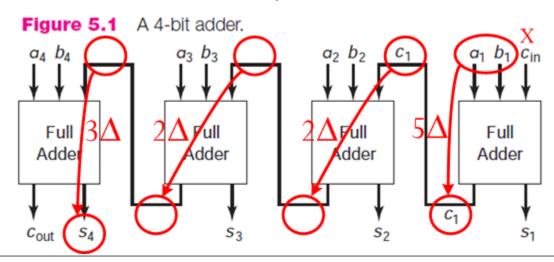

- If we wish to build an *n*-bit adder, we need only connect *n* of these. A 4-bit version is shown in Fig. 5.1

# Delay in Combinational Logic Circuits (1/4)

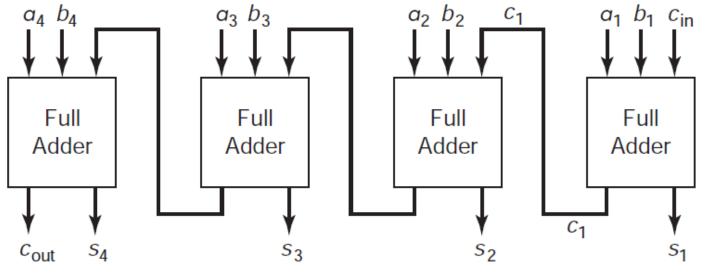

When the input to a gate changes, the output of that gate does not change instantaneously, but there is a small delay, Δ.

If the output of one gate is used as the input to another, the delays add

Figure 5.2 Illustration of gate delay.

# Delay in Combinational Logic Circuits (2/4)

- The output is stable after the longest delay path. We are not usually interested in the output until it is stable

- Consider the *full adder*. It adds two 1-bit numbers and a carry input from the next less significant digit and produces a sum bit and a carry out to the next more significant digit

- We assume that all inputs are available at the same time and the processing delay of a gate is Δ. If two inputs to a gate change at different times, the output may change as late as Δ after the last input changes

# Delay in Combinational Logic Circuits (3/4)

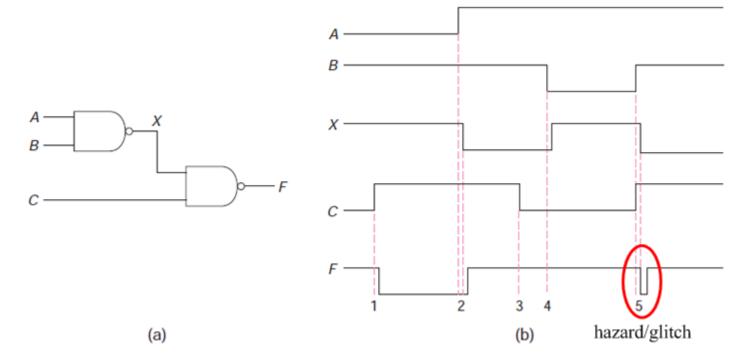

- Figure 5.3 shows four critical paths and their time delays in terms of  $\Delta$

# Delay in Combinational Logic Circuits (4/4)

- The total time delay required for an *n*-bit adder (carry-ripple adder) is calculated as the delay from the inputs to c<sub>out</sub> (for the least significant bit), plus *n*-2 times the delay from c<sub>in</sub> to c<sub>out</sub> (for the middle full adders), plus the longer of the delay from c<sub>in</sub> to s (for the most significant bit). That equals 5Δ+ (*n*-2)×2Δ+3Δ=(2*n*+4)Δ

- For a 64-bit adder, the delay would be  $132\Delta$

# Adders (1/4)

- One approach to building an *n*-bit adder is to connect together *n* 1-bit adders. This is referred to as a carry-ripple adder. The time for the output of the adder to become stable is as large as  $(2n+4)\Delta$

- To speed this up, several approaches have been proposed.

One approach is to implement a multi-bit adder with an SOP expression

- The truth table for a 2-bit adder is shown in Table 5.1, where  $a_1$  and  $b_1$  are the low-order bits

### Adders (2/4)

• The minimum SOP expressions are  $c_{out} = a_2b_2 + a_1b_1a_2 + a_1b_1b_2 + c_{in}b_1b_2 + c_{in}b_1a_2 + c_{in}a_1b_2$

$+ c_{in}a_1a_2$

$$s_{2} = a_{1}b_{1}a'_{2}b'_{2} + a_{1}b_{1}a_{2}b_{2} + c'_{in}a'_{1}a'_{2}b_{2} + c'_{in}a'_{1}a_{2}b'_{2} + c'_{in}b'_{1}a'_{2}b_{2} + c'_{in}b'_{1}a_{2}b'_{2} + a'_{1}b'_{1}a_{2}b'_{2} + a'_{1}b'_{1}a'_{2}b_{2} + c_{in}b_{1}a'_{2}b'_{2} + c_{in}b_{1}a_{2}b_{2} + c_{in}a_{1}a'_{2}b'_{2} + c_{in}a_{1}a_{2}b_{2}$$

$$s_1 = c'_{\text{in}}a'_1b_1 + c'_{\text{in}}a_1b'_1 + c_{\text{in}}a'_1b'_1 + c_{\text{in}}a_1b_1$$

Table 5.1

Two-bit adder truth table.

| a22 | $b_2$ | $a_1$ | <b>b</b> <sub>1</sub> | C <sub>in</sub> | C <sub>out</sub> | <i>s</i> <sub>2</sub> | <i>s</i> <sub>1</sub> |

|-----|-------|-------|-----------------------|-----------------|------------------|-----------------------|-----------------------|

| 0   | 0     | 0     | 0                     | 0               | 0                | 0                     | 0                     |

| 0   | 0     | 0     | 0                     | 1               | 0                | 0                     | 1                     |

| 0   | 0     | 0     | 1                     | 0               | 0                | 0                     | 1                     |

| 0   | 0     | 0     | 1                     | 1               | 0                | 1                     | 0                     |

| 0   | 0     | 1     | 0                     | 0               | 0                | 0                     | 1                     |

| 0   | 0     | 1     | 0                     | 1               | 0                | 1                     | 0                     |

|     |       |       | 22                    |                 |                  |                       |                       |

| 1   | 1     | 1     | 0                     | 1               | 1                | 1                     | 0                     |

| 1   | 1     | 1     | 1                     | 0               | 1                | 1                     | 0                     |

| 1   | 1     | 1     | 1                     | 1               | 1                | 1                     | 1                     |

# Adders (3/4)

- This two-level solution requires a 12-input gate for *s*<sub>2</sub>. Clearly, we could repeat this process for a 3-bit or 4-bit adder, but the algebra gets very complex, and the number of terms increases drastically

- Another problem that we would encounter in this implementation is there is a limitation on the number of inputs (called *fan-in*) for a gate. Gates with 12 inputs may not be practical or may encounter delays of greater than  $\Delta$

## Adders (4/4)

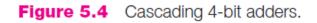

- There are 4-bit adders: the 7483, 7483A, and 74283. Each is implemented differently, with a three-level circuit for the carry-out. The total delay for an *n*-bit adder reaches  $(3/4n+1)\Delta$

- When larger adders are needed, these 4-bit adders can be *cascaded*. For example, a 12-bit adder, using three 4-bit adders

## Subtractors and Adder (1/2)

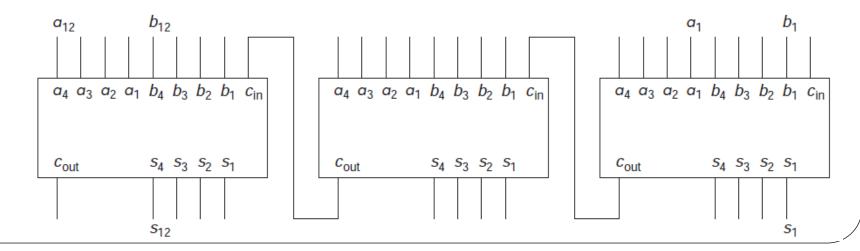

- To build an adder/subtractor, we need a signal line that is 0 for addition and 1 for subtraction. We call that *a*'/*s* (short for add'/subtractor)

- Remember that

$1 \bigoplus x = x'$  and  $0 \bigoplus x = x$

• In Fig. 5-5, the input bits  $b_i$ , i=1,2,3,4, are connected through Exclusive-OR gates enabled by a'/s. The numbering format is 2's complement

#### Subtractors and Adder (2/2)

Figure 5.5 A 4-bit adder/subtractor.

# Comparators (1/2)

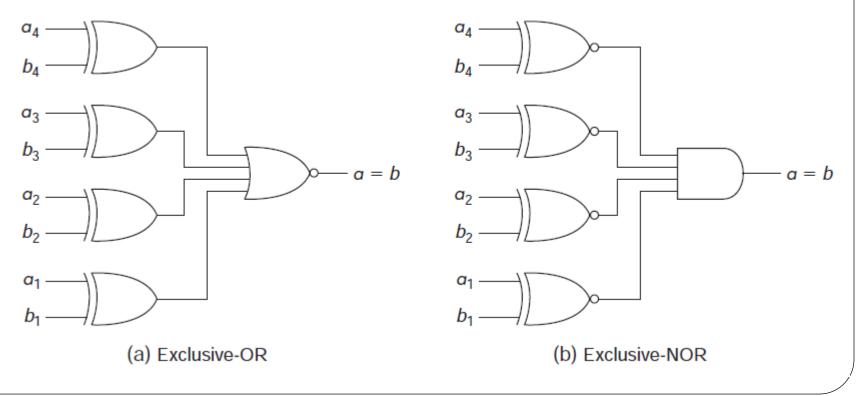

• The Exclusive-OR produces a 1 if the two inputs are unequal and a 0, otherwise. Mutli-bit numbers are unequal if any of the input pairs are unequal.

Figure 5.6 Two 4-bit comparators.

14

### Comparators (2/2)

- To build a 4-bit comparator that will indicate greater than and less than, as well as equal to (for unsigned numbers), we recognize that, starting at the most significant bit ( $a_4$  and  $b_4$ )

- a > b if  $a_4 > b_4$  or  $(a_4 = b_4 \text{ and } a_3 > b_3)$  or  $(a_4 = b_4 \text{ and} a_3 = b_3 \text{ and } a_2 > b_2)$  or  $(a_4 = b_4 \text{ and } a_3 = b_3 \text{ and } a_2 = b_2 \text{ and} a_1 > b_1)$

- a < b if  $a_4 < b_4$  or  $(a_4 = b_4 \text{ and } a_3 < b_3)$  or  $(a_4 = b_4 \text{ and } a_3 = b_3 \text{ and } a_2 < b_2)$  or  $(a_4 = b_4 \text{ and } a_3 = b_3 \text{ and } a_2 = b_2 \text{ and } a_1 < b_1)$

• a = b if  $a_4 = b_4$  and  $a_3 = b_3$  and  $a_2 = b_2$  and  $a_1 = b_1$

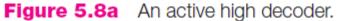

# Binary Decoders (1/7)

- A *binary decoder* is a device that, when activated, selects one of several output lines, based on a coded input signal. Most commonly, the input is an *n*-bit binary number, and there are up to 2<sup>*n*</sup> output lines

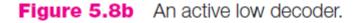

- Fig. 5.8a is an active high decoder, while Fig. 5.8b is an active low decoder

### Binary Decoders (2/7)

17

#### Binary Decoders (3/7)

# Binary Decoders (4/7)

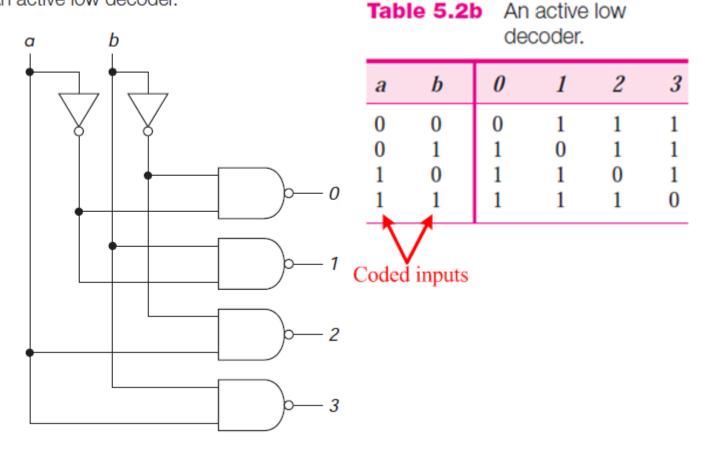

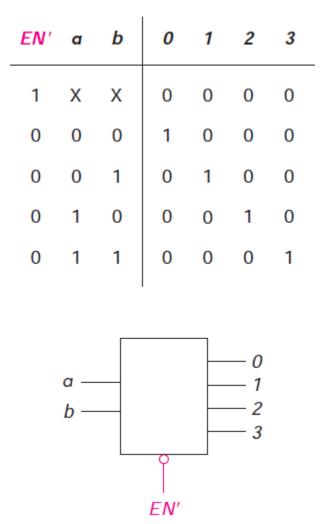

- The circuit for an active high output decoder with an active low enable input is shown in Fig. 5.9. Note the enable input is inverted and connected to each AND gate. When *EN*'=1, a 0 is on the input to each AND gate, and, thus, all of the AND gate outputs are 0

- In most commercial literature, such signals are labeled with an overbar *EN*, rather than as *EN*'

### Binary Decoders (5/7)

Figure 5.9 Decoder with enable.

## Binary Decoders (6/7)

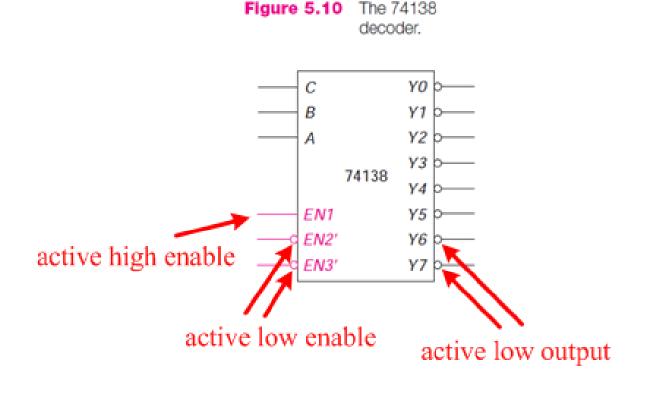

• A truth table for the 74138 is shown in Table 5.3 and the block diagram is shown in Fig. 5.10

## Binary Decoders (7/7)

| Table 5.3 | The 74138 decoder. |

|-----------|--------------------|

|-----------|--------------------|

| E   | Enables |      | Inputs |   | Outputs |    |    |    |           |    |    |    |    |

|-----|---------|------|--------|---|---------|----|----|----|-----------|----|----|----|----|

| EN1 | EN2'    | EN3' | С      | В | A       | YO | Y1 | Y2 | <i>Y3</i> | Y4 | ¥5 | ¥6 | Y7 |

| 0   | Х       | Х    | Х      | Х | Х       | 1  | 1  | 1  | 1         | 1  | 1  | 1  | 1  |

| Х   | 1       | Х    | Х      | Х | Х       | 1  | 1  | 1  | 1         | 1  | 1  | 1  | 1  |

| Х   | Х       | 1    | Х      | Х | Х       | 1  | 1  | 1  | 1         | 1  | 1  | 1  | 1  |

| 1   | 0       | 0    | 0      | 0 | 0       | 0  | 1  | 1  | 1         | 1  | 1  | 1  | 1  |

| 1   | 0       | 0    | 0      | 0 | 1       | 1  | 0  | 1  | 1         | 1  | 1  | 1  | 1  |

| 1   | 0       | 0    | 0      | 1 | 0       | 1  | 1  | 0  | 1         | 1  | 1  | 1  | 1  |

| 1   | 0       | 0    | 0      | 1 | 1       | 1  | 1  | 1  | 0         | 1  | 1  | 1  | 1  |

| 1   | 0       | 0    | 1      | 0 | 0       | 1  | 1  | 1  | 1         | 0  | 1  | 1  | 1  |

| 1   | 0       | 0    | 1      | 0 | 1       | 1  | 1  | 1  | 1         | 1  | 0  | 1  | 1  |

| 1   | 0       | 0    | 1      | 1 | 0       | 1  | 1  | 1  | 1         | 1  | 1  | 0  | 1  |

| 1   | 0       | 0    | 1      | 1 | 1       | 1  | 1  | 1  | 1         | 1  | 1  | 1  | 0  |